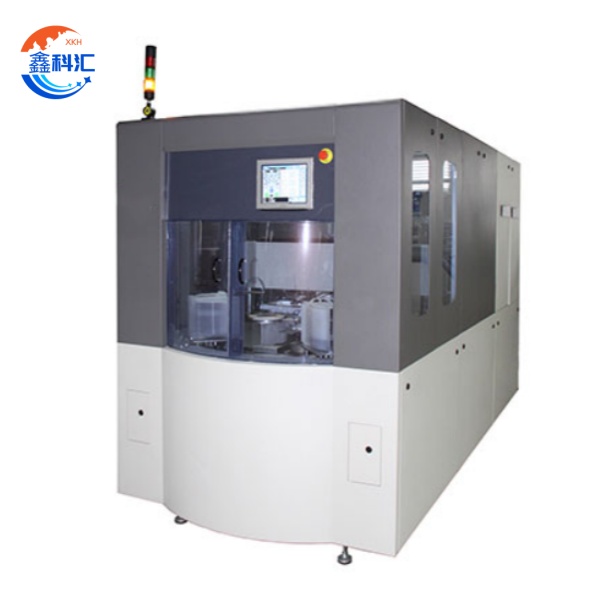

Wafer-Dünnungsanlage für die Bearbeitung von 4- bis 12-Zoll-Saphir-/SiC-/Si-Wafern

Funktionsprinzip

Der Wafer-Dünnungsprozess verläuft in drei Phasen:

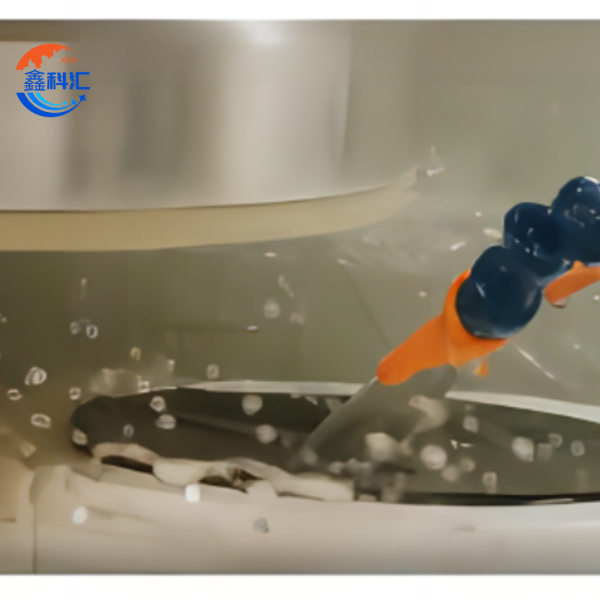

Grobschleifen: Eine Diamantscheibe (Korngröße 200–500 μm) trägt bei 3000–5000 U/min 50–150 μm Material ab, um die Dicke schnell zu reduzieren.

Feinschleifen: Eine feinere Schleifscheibe (Korngröße 1–50 μm) reduziert die Dicke auf 20–50 μm bei <1 μm/s, um Schäden unter der Oberfläche zu minimieren.

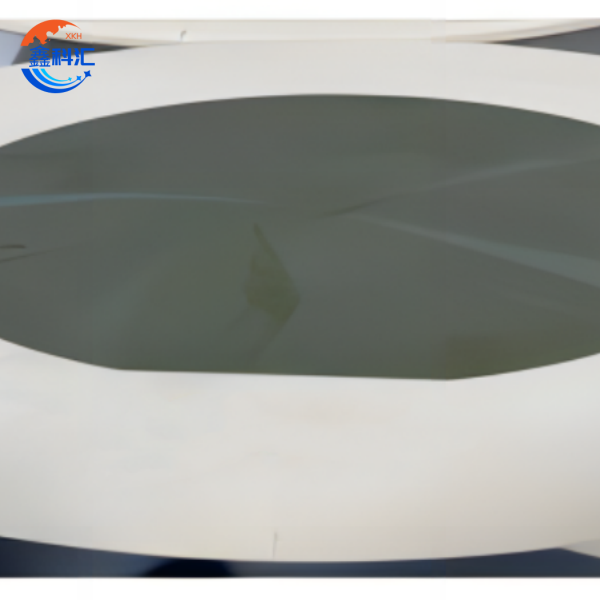

Polieren (CMP): Eine chemisch-mechanische Suspension beseitigt Restschäden und erzielt eine Oberflächenrauheit von Ra <0,1 nm.

Kompatible Materialien

Silizium (Si): Standard für CMOS-Wafer, auf 25 μm für 3D-Stapelung ausgedünnt.

Siliziumkarbid (SiC): Erfordert spezielle Diamantschleifscheiben (80% Diamantkonzentration) für die thermische Stabilität.

Saphir (Al₂O₃): Ausgedünnt auf 50 μm für UV-LED-Anwendungen.

Kernsystemkomponenten

1. Mahlsystem

Zweiachsige Schleifmaschine: Kombiniert Grob- und Feinschleifen auf einer einzigen Plattform und reduziert so die Zykluszeit um 40 %.

Aerostatische Spindel: Drehzahlbereich 0–6000 U/min mit einem Rundlauffehler von <0,5 μm.

2. Wafer-Handhabungssystem

Vakuumspannfutter: Haltekraft >50 N bei einer Positioniergenauigkeit von ±0,1 μm.

Roboterarm: Transportiert 4–12-Zoll-Wafer mit einer Geschwindigkeit von 100 mm/s.

3. Steuerungssystem

Laserinterferometrie: Echtzeit-Dickenüberwachung (Auflösung 0,01 μm).

KI-gestütztes Feedforward: Prognostiziert den Radverschleiß und passt Parameter automatisch an.

4. Kühlung & Reinigung

Ultraschallreinigung: Entfernt Partikel >0,5 μm mit einer Effizienz von 99,9 %.

Deionisiertes Wasser: Kühlt die Waffel auf <5°C über Umgebungstemperatur.

Kernvorteile

1. Ultrahohe Präzision: TTV (Gesamtdickenvariation) <0,5 μm, WTW (Dickenvariation innerhalb des Wafers) <1 μm.

2. Integration mehrerer Prozesse: Kombiniert Schleifen, CMP und Plasmaätzen in einer Maschine.

3. Materialverträglichkeit:

Silizium: Reduzierung der Dicke von 775 μm auf 25 μm.

SiC: Erreicht eine TTV von <2 μm für HF-Anwendungen.

Dotierte Wafer: Phosphor-dotierte InP-Wafer mit einer Widerstandsdrift von <5%.

4. Intelligente Automatisierung: Die MES-Integration reduziert menschliche Fehler um 70 %.

5. Energieeffizienz: 30 % geringerer Stromverbrauch durch regenerative Bremsung.

Wichtigste Anwendungsbereiche

1. Fortschrittliche Verpackungstechnologie

• 3D-ICs: Durch die Waferverdünnung wird das vertikale Stapeln von Logik-/Speicherchips (z. B. HBM-Stacks) ermöglicht. Dadurch wird eine zehnfach höhere Bandbreite und ein um 50 % reduzierter Stromverbrauch im Vergleich zu 2,5D-Lösungen erzielt. Die Anlagen unterstützen Hybrid-Bonding und TSV-Integration (Through-Silicon Via), die für KI/ML-Prozessoren mit einem Verbindungsabstand von <10 µm unerlässlich sind. Beispielsweise ermöglichen 12-Zoll-Wafer mit einer Dicke von 25 µm das Stapeln von mehr als acht Lagen bei einer Verformung von <1,5 %, was für LiDAR-Systeme in der Automobilindustrie essenziell ist.

• Fan-Out-Packaging: Durch die Reduzierung der Waferdicke auf 30 μm wird die Verbindungslänge um 50 % verkürzt, wodurch die Signalverzögerung minimiert (<0,2 ps/mm) und ultradünne 0,4 mm Chiplets für mobile SoCs ermöglicht werden. Das Verfahren nutzt spannungskompensierte Schleifalgorithmen, um Verformungen zu vermeiden (TTV-Kontrolle >50 μm) und so die Zuverlässigkeit in Hochfrequenz-HF-Anwendungen zu gewährleisten.

2. Leistungselektronik

• IGBT-Module: Durch die Reduzierung der Dicke auf 50 µm wird der Wärmewiderstand auf <0,5 °C/W gesenkt, wodurch 1200-V-SiC-MOSFETs bei Sperrschichttemperaturen von 200 °C betrieben werden können. Unsere Anlagen nutzen mehrstufiges Schleifen (grob: 46 µm Körnung → fein: 4 µm Körnung), um Beschädigungen der Oberfläche zu vermeiden und eine Zuverlässigkeit von >10.000 Temperaturwechselzyklen zu erreichen. Dies ist entscheidend für Wechselrichter in Elektrofahrzeugen, da 10 µm dicke SiC-Wafer die Schaltgeschwindigkeit um 30 % verbessern.

• GaN-auf-SiC-Leistungshalbleiter: Die Waferverdünnung auf 80 μm erhöht die Elektronenbeweglichkeit (μ > 2000 cm²/V·s) von 650-V-GaN-HEMTs und reduziert die Leitungsverluste um 18 %. Das Verfahren nutzt lasergestütztes Vereinzeln, um Risse während der Verdünnung zu vermeiden und eine Kantenausfransung von < 5 μm für HF-Leistungsverstärker zu erreichen.

3. Optoelektronik

• GaN-auf-SiC-LEDs: 50 µm dicke Saphirsubstrate verbessern die Lichtausbeute (LEE) auf 85 % (gegenüber 65 % bei 150 µm dicken Wafern) durch Minimierung der Photoneneinfangung. Die extrem niedrige TTV-Kontrolle unserer Anlage (< 0,3 µm) gewährleistet eine gleichmäßige LED-Emission auf 12-Zoll-Wafern – entscheidend für Micro-LED-Displays, die eine Wellenlängenhomogenität von < 100 nm erfordern.

• Siliziumphotonik: 25 µm dicke Siliziumwafer ermöglichen um 3 dB/cm geringere Ausbreitungsverluste in Wellenleitern, was für optische Transceiver mit 1,6 Tbit/s unerlässlich ist. Das Verfahren integriert eine CMP-Glättung zur Reduzierung der Oberflächenrauheit auf Ra < 0,1 nm und steigert so die Kopplungseffizienz um 40 %.

4. MEMS-Sensoren

• Beschleunigungsmesser: 25 µm dicke Siliziumwafer erreichen ein Signal-Rausch-Verhältnis (SNR) von über 85 dB (gegenüber 75 dB bei 50 µm dicken Wafern) durch erhöhte Empfindlichkeit gegenüber der Verschiebung der Prüfmasse. Unser Zweiachsen-Schleifsystem kompensiert Spannungsgradienten und gewährleistet eine Empfindlichkeitsdrift von unter 0,5 % im Temperaturbereich von -40 °C bis 125 °C. Anwendungsgebiete sind die Erkennung von Fahrzeugunfällen und die Bewegungsverfolgung in AR/VR-Systemen.

• Drucksensoren: Durch die Reduzierung der Dicke auf 40 μm werden Messbereiche von 0–300 bar mit einer Hysterese von <0,1 % des Messbereichsendwertes ermöglicht. Mithilfe temporärer Verbindungen (Glasträger) wird ein Waferbruch während des Ätzens der Rückseite vermieden, wodurch eine Überdrucktoleranz von <1 μm für industrielle IoT-Sensoren erreicht wird.

• Technische Synergie: Unsere Wafer-Dünnungsanlage vereint mechanisches Schleifen, CMP und Plasmaätzen, um unterschiedlichste Materialherausforderungen (Si, SiC, Saphir) zu bewältigen. Beispielsweise erfordert GaN auf SiC ein Hybrid-Schleifen (Diamantscheiben + Plasma), um Härte und Wärmeausdehnung auszugleichen, während MEMS-Sensoren eine Oberflächenrauheit von unter 5 nm durch CMP-Polieren benötigen.

• Branchenauswirkungen: Durch die Ermöglichung dünnerer, leistungsstärkerer Wafer treibt diese Technologie Innovationen bei KI-Chips, 5G mmWave-Modulen und flexibler Elektronik voran, mit TTV-Toleranzen von <0,1 μm für faltbare Displays und <0,5 μm für LiDAR-Sensoren im Automobilbereich.

Dienstleistungen von XKH

1. Kundenspezifische Lösungen

Skalierbare Konfigurationen: Kammerdesigns mit 4–12 Zoll Durchmesser und automatisierter Be- und Entladung.

Dotierungsunterstützung: Kundenspezifische Rezepturen für Er/Yb-dotierte Kristalle und InP/GaAs-Wafer.

2. Umfassender Support

Prozessentwicklung: Kostenlose Testläufe mit Optimierung.

Globales Training: Jährlich stattfindende technische Workshops zu Wartung und Fehlerbehebung.

3. Mehrkomponentenverarbeitung

SiC: Waferverdünnung auf 100 μm mit Ra <0,1 nm.

Saphir: 50 μm Dicke für UV-Laserfenster (Transmissionsgrad >92 % bei 200 nm).

4. Mehrwertdienste

Verbrauchsmaterialien: Diamantschleifscheiben (2000+ Wafer/Lebensdauer) und CMP-Slurries.

Abschluss

Diese Wafer-Dünnungsanlage bietet branchenführende Präzision, Vielseitigkeit für verschiedene Materialien und intelligente Automatisierung und ist damit unverzichtbar für die 3D-Integration und Leistungselektronik. Die umfassenden Dienstleistungen von XKH – von der kundenspezifischen Anpassung bis zur Nachbearbeitung – gewährleisten Kosteneffizienz und herausragende Leistung in der Halbleiterfertigung.