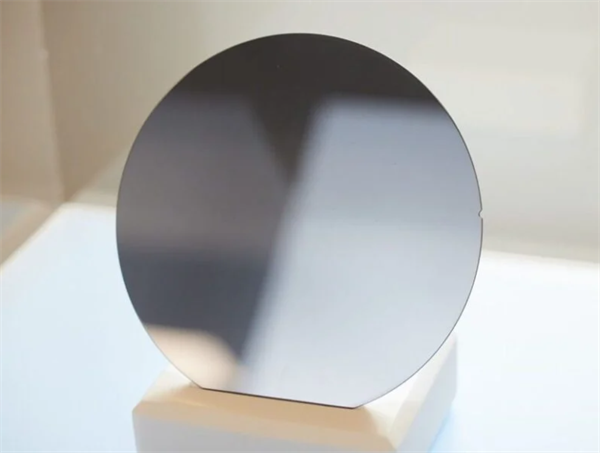

P-Typ SiC-Wafer 4H/6H-P 3C-N 6 Zoll Dicke 350 μm mit primärer flacher Orientierung

Spezifikation 4H/6H-P Typ SiC-Verbundsubstrate Tabelle mit allgemeinen Parametern

6 Siliziumkarbid (SiC)-Substrat mit Zoll Durchmesser Spezifikation

| Grad | Null MPD-ProduktionNote (Z Grad) | StandardproduktionNote (P) Grad) | Dummy-Note (D Grad) | ||

| Durchmesser | 145,5 mm bis 150,0 mm | ||||

| Dicke | 350 μm ± 25 μm | ||||

| Wafer-Ausrichtung | -OffAchse: 2,0°–4,0° in Richtung [1120] ± 0,5° für 4H/6H-P, On-Achse:〈111〉± 0,5° für 3C-N | ||||

| Mikrorohrdichte | 0 cm-2 | ||||

| Widerstand | p-Typ 4H/6H-P | ≤0,1 Ωꞏcm | ≤0,3 Ωꞏcm | ||

| n-Typ 3C-N | ≤0,8 mΩꞏcm | ≤1 m Ωꞏcm | |||

| Primäre flache Ausrichtung | 4H/6H-P | -{1010} ± 5,0° | |||

| 3C-N | -{110} ± 5,0° | ||||

| Primäre Flachlänge | 32,5 mm ± 2,0 mm | ||||

| Sekundäre Flachlänge | 18,0 mm ± 2,0 mm | ||||

| Sekundäre flache Ausrichtung | Siliziumseite nach oben: 90° im Uhrzeigersinn von der planaren Seite ± 5,0° | ||||

| Kantenausschluss | 3 mm | 6 mm | |||

| LTV/TTV/Bow /Warp | ≤2,5 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||

| Rauheit | Polnische Ra≤1 nm | ||||

| CMP Ra≤0,2 nm | Ra≤0,5 nm | ||||

| Kantenrisse durch hochintensives Licht | Keiner | Gesamtlänge ≤ 10 mm, Einzellänge ≤ 2 mm | |||

| Sechseckige Platten durch Hochleistungslicht | Kumulative Fläche ≤0,05% | Kumulative Fläche ≤0,1% | |||

| Polytypbereiche durch hochintensives Licht | Keiner | Kumulative Fläche ≤ 3 % | |||

| Visuelle Kohlenstoffeinschlüsse | Kumulative Fläche ≤0,05% | Kumulative Fläche ≤3% | |||

| Kratzer auf Silikonoberflächen durch hochintensives Licht | Keiner | Gesamtlänge ≤ 1 × Waferdurchmesser | |||

| Kantenchips mit hoher Lichtintensität | Keine zulässigen Breiten und Tiefen ≥ 0,2 mm. | 5 zulässig, jeweils ≤1 mm | |||

| Silizium-Oberflächenkontamination durch hohe Intensität | Keiner | ||||

| Verpackung | Mehrfachwaffelkassette oder Einzelwaffelbehälter | ||||

Anmerkungen:

※ Die Grenzwerte für Defekte gelten für die gesamte Waferoberfläche mit Ausnahme des Randbereichs. # Die Kratzer sollten auf der Si-Seite überprüft werden.

Der p-dotierte SiC-Wafer 4H/6H-P 3C-N mit seinen 6 Zoll Abmessungen und 350 µm Dicke spielt eine entscheidende Rolle in der industriellen Fertigung von Hochleistungselektronik. Seine exzellente Wärmeleitfähigkeit und hohe Durchbruchspannung machen ihn ideal für die Herstellung von Komponenten wie Leistungsschaltern, Dioden und Transistoren, die in Hochtemperaturumgebungen wie Elektrofahrzeugen, Stromnetzen und Systemen für erneuerbare Energien eingesetzt werden. Die Fähigkeit des Wafers, auch unter rauen Bedingungen effizient zu arbeiten, gewährleistet zuverlässige Leistung in industriellen Anwendungen, die eine hohe Leistungsdichte und Energieeffizienz erfordern. Darüber hinaus ermöglicht seine primäre Planarität eine präzise Ausrichtung bei der Bauelementefertigung und verbessert so die Produktionseffizienz und Produktkonsistenz.

Zu den Vorteilen von SiC-Verbundsubstraten vom N-Typ gehören

- Hohe WärmeleitfähigkeitP-dotierte SiC-Wafer leiten Wärme effizient ab und eignen sich daher ideal für Hochtemperaturanwendungen.

- Hohe Durchschlagsspannung: Hält hohen Spannungen stand und gewährleistet so die Zuverlässigkeit in der Leistungselektronik und in Hochspannungsgeräten.

- Widerstandsfähigkeit gegenüber rauen UmgebungenHervorragende Beständigkeit unter extremen Bedingungen wie hohen Temperaturen und korrosiven Umgebungen.

- Effiziente LeistungsumwandlungDie P-Dotierung ermöglicht eine effiziente Leistungsübertragung und macht den Wafer somit für Energieumwandlungssysteme geeignet.

- Primäre flache AusrichtungGewährleistet eine präzise Ausrichtung während der Fertigung und verbessert so die Genauigkeit und Konsistenz des Geräts.

- Dünne Struktur (350 μm)Die optimale Dicke des Wafers ermöglicht die Integration in fortschrittliche, platzsparende elektronische Bauelemente.

Insgesamt bietet der P-dotierte SiC-Wafer 4H/6H-P 3C-N eine Reihe von Vorteilen, die ihn ideal für industrielle und elektronische Anwendungen machen. Seine hohe Wärmeleitfähigkeit und Durchbruchspannung ermöglichen einen zuverlässigen Betrieb in Hochtemperatur- und Hochspannungsumgebungen, während seine Beständigkeit gegenüber rauen Bedingungen Langlebigkeit gewährleistet. Die P-Dotierung ermöglicht eine effiziente Leistungsumwandlung und macht ihn somit ideal für Leistungselektronik und Energiesysteme. Darüber hinaus gewährleistet die primäre Planarorientierung des Wafers eine präzise Ausrichtung während des Herstellungsprozesses und verbessert so die Produktionskonsistenz. Mit einer Dicke von 350 µm eignet er sich hervorragend für die Integration in moderne, kompakte Bauelemente.

Detailliertes Diagramm