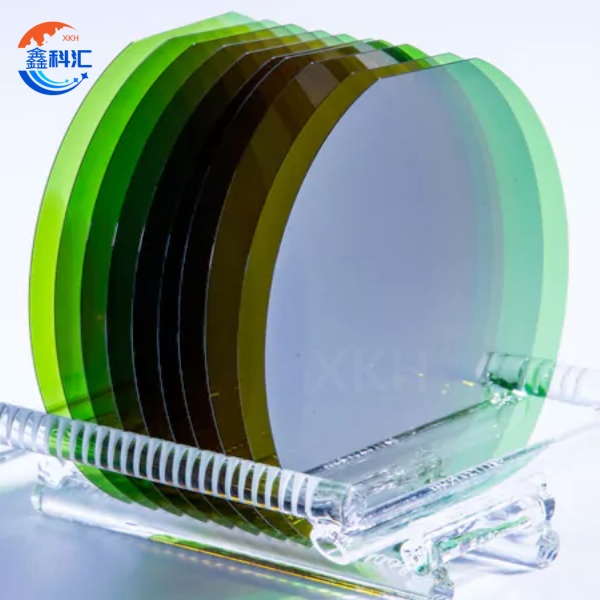

12-Zoll-SiC-Substrat, N-Typ, große Abmessungen, Hochleistungs-HF-Anwendungen

Technische Parameter

| Spezifikation für ein 12-Zoll-Siliziumkarbid-(SiC)-Substrat | |||||

| Grad | ZeroMPD Produktion Note (Z-Note) | Standardproduktion Note (P-Note) | Dummy-Note (Note D) | ||

| Durchmesser | 3 0 0 mm~1305 mm | ||||

| Dicke | 4H-N | 750 μm ± 15 μm | 750 μm ± 25 μm | ||

| 4H-SI | 750 μm ± 15 μm | 750 μm ± 25 μm | |||

| Wafer-Ausrichtung | Außerhalb der Achse: 4,0° in Richtung <1120> ± 0,5° für 4H-N, auf der Achse: <0001> ± 0,5° für 4H-SI | ||||

| Mikrorohrdichte | 4H-N | ≤0,4 cm-2 | ≤4cm-2 | ≤25cm-2 | |

| 4H-SI | ≤5cm-2 | ≤10cm-2 | ≤25cm-2 | ||

| Widerstand | 4H-N | 0,015–0,024 Ω·cm | 0,015~0,028 Ω·cm | ||

| 4H-SI | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |||

| Primäre flache Ausrichtung | {10-10} ±5,0° | ||||

| Primäre Flachlänge | 4H-N | N / A | |||

| 4H-SI | Kerbe | ||||

| Kantenausschluss | 3 mm | ||||

| LTV/TTV/Bow /Warp | ≤5μm/≤15μm/≤35 μm/≤55 μm | ≤5μm/≤15μm/≤35 □μm/≤55 □μm | |||

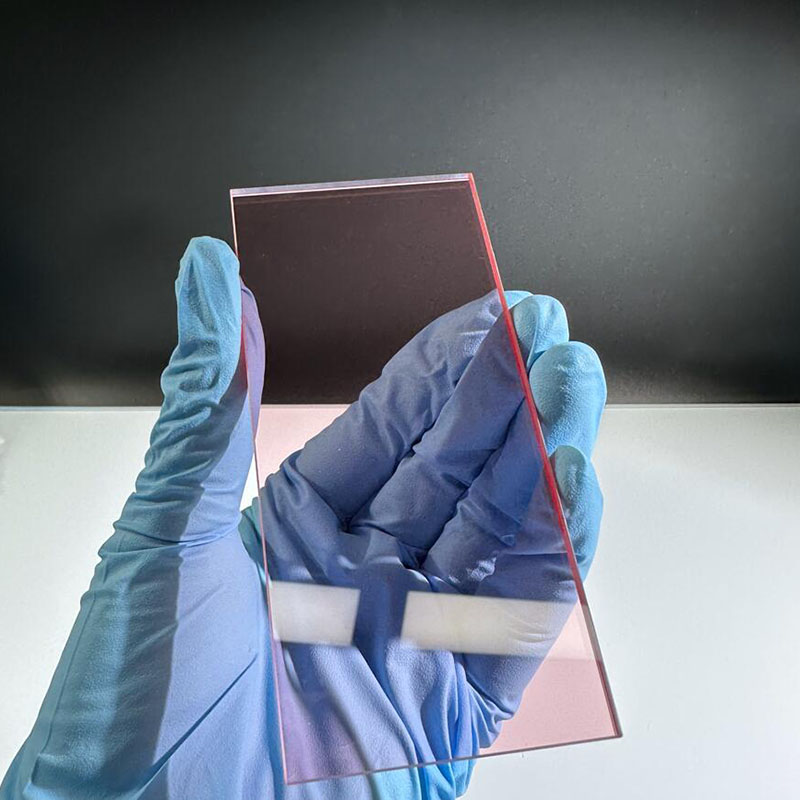

| Rauheit | Polnische Ra≤1 nm | ||||

| CMP Ra≤0,2 nm | Ra≤0,5 nm | ||||

| Kantenrisse durch hochintensives Licht Sechseckige Platten durch Hochleistungslicht Polytypbereiche durch hochintensives Licht Visuelle Kohlenstoffeinschlüsse Kratzer auf Silikonoberflächen durch hochintensives Licht | Keiner Kumulative Fläche ≤0,05% Keiner Kumulative Fläche ≤0,05% Keiner | Gesamtlänge ≤ 20 mm, Einzellänge ≤ 2 mm Kumulative Fläche ≤0,1% Kumulative Fläche ≤ 3 % Kumulative Fläche ≤3% Gesamtlänge ≤ 1 × Waferdurchmesser | |||

| Kantensplitter durch hochintensives Licht | Keine zulässige Breite und Tiefe ≥ 0,2 mm. | 7 zulässig, jeweils ≤1 mm | |||

| (TSD) Schraubenverrenkung | ≤500 cm-2 | N / A | |||

| (BPD) Basisebenenversetzung | ≤1000 cm-2 | N / A | |||

| Siliziumoberflächenkontamination durch hochintensives Licht | Keiner | ||||

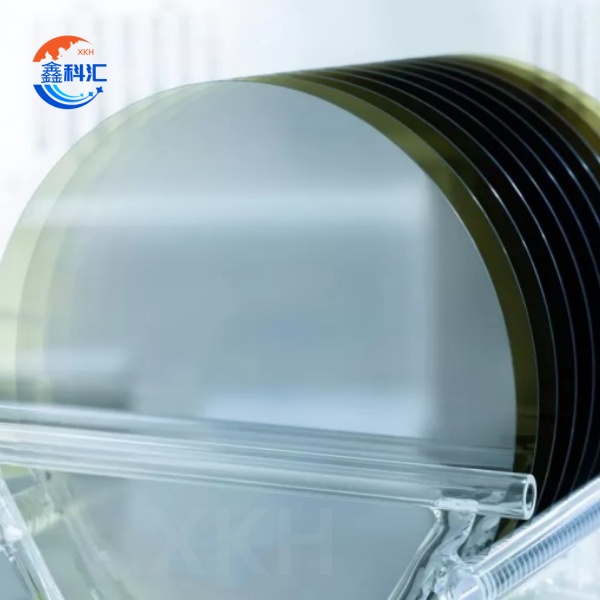

| Verpackung | Mehrfachwaffelkassette oder Einzelwaffelbehälter | ||||

| Anmerkungen: | |||||

| 1 Die Grenzwerte für Defekte gelten für die gesamte Waferoberfläche mit Ausnahme des Randausschlussbereichs. 2Die Kratzer sollten nur auf der Si-Seite überprüft werden. 3 Die Versetzungsdaten stammen ausschließlich von mit KOH geätzten Wafern. | |||||

Hauptmerkmale

1. Vorteil der größeren Größe: Das 12-Zoll-SiC-Substrat (12-Zoll-Siliziumkarbid-Substrat) bietet eine größere Fläche pro Wafer, wodurch mehr Chips pro Wafer hergestellt werden können. Dies senkt die Herstellungskosten und erhöht die Ausbeute.

2. Hochleistungsmaterial: Die hohe Temperaturbeständigkeit und die hohe Durchschlagsfeldstärke von Siliziumkarbid machen das 12-Zoll-Substrat ideal für Hochspannungs- und Hochfrequenzanwendungen wie EV-Wechselrichter und Schnellladesysteme.

3. Verarbeitungskompatibilität: Trotz der hohen Härte und der damit verbundenen Verarbeitungsherausforderungen weist das 12-Zoll-SiC-Substrat dank optimierter Schneid- und Poliertechniken eine geringere Anzahl an Oberflächenfehlern auf, was die Geräteausbeute verbessert.

4. Überlegenes Wärmemanagement: Dank der besseren Wärmeleitfähigkeit im Vergleich zu siliziumbasierten Materialien wird die Wärmeableitung in Hochleistungsgeräten effektiv optimiert, wodurch die Lebensdauer der Geräte verlängert wird.

Hauptanwendungen

1. Elektrofahrzeuge: Das 12-Zoll-SiC-Substrat (12-Zoll-Siliziumkarbid-Substrat) ist eine Kernkomponente von elektrischen Antriebssystemen der nächsten Generation und ermöglicht hocheffiziente Wechselrichter, die die Reichweite erhöhen und die Ladezeit verkürzen.

2. 5G-Basisstationen: Großflächige SiC-Substrate unterstützen Hochfrequenz-HF-Bauelemente und erfüllen die Anforderungen von 5G-Basisstationen an hohe Leistung und geringe Verluste.

3. Industrielle Stromversorgungen: In Solarwechselrichtern und intelligenten Stromnetzen kann das 12-Zoll-Substrat höheren Spannungen standhalten und gleichzeitig den Energieverlust minimieren.

4. Unterhaltungselektronik: Zukünftige Schnellladegeräte und Netzteile für Rechenzentren könnten 12-Zoll-SiC-Substrate verwenden, um eine kompakte Größe und höhere Effizienz zu erreichen.

Dienstleistungen von XKH

Wir sind spezialisiert auf kundenspezifische Bearbeitungsdienstleistungen für 12-Zoll-SiC-Substrate (12-Zoll-Siliziumkarbid-Substrate), einschließlich:

1. Vereinzeln und Polieren: Substratbearbeitung mit geringer Beschädigung und hoher Planheit, abgestimmt auf die Kundenanforderungen, um eine stabile Bauteilleistung zu gewährleisten.

2. Unterstützung des epitaktischen Wachstums: Hochwertige Dienstleistungen für epitaktische Wafer zur Beschleunigung der Chipherstellung.

3. Prototyping in Kleinserien: Unterstützt die Validierung von F&E-Projekten für Forschungseinrichtungen und Unternehmen und verkürzt die Entwicklungszyklen.

4. Technische Beratung: Komplettlösungen von der Materialauswahl bis zur Prozessoptimierung, die Kunden helfen, Herausforderungen bei der SiC-Verarbeitung zu meistern.

Ob für die Massenproduktion oder spezielle Anpassungen – unsere 12-Zoll-SiC-Substrat-Services sind auf Ihre Projektanforderungen abgestimmt und ermöglichen technologische Fortschritte.