SOI-Wafer (Silicon-On-Insulator)Es handelt sich um ein spezielles Halbleitermaterial mit einer ultradünnen Siliziumschicht auf einer isolierenden Oxidschicht. Diese einzigartige Sandwichstruktur ermöglicht deutliche Leistungssteigerungen bei Halbleiterbauelementen.

Strukturelle Zusammensetzung:

Geräteschicht (oberes Silizium):

Die Dicke variiert von wenigen Nanometern bis zu Mikrometern und dient als aktive Schicht für die Transistorherstellung.

Vergrabene Oxidschicht (KASTEN):

Eine Siliziumdioxid-Isolierschicht (0,05-15 μm dick), die die Geräteschicht elektrisch vom Substrat isoliert.

Basissubstrat:

Massives Silizium (100-500 μm dick) dient als mechanische Stütze.

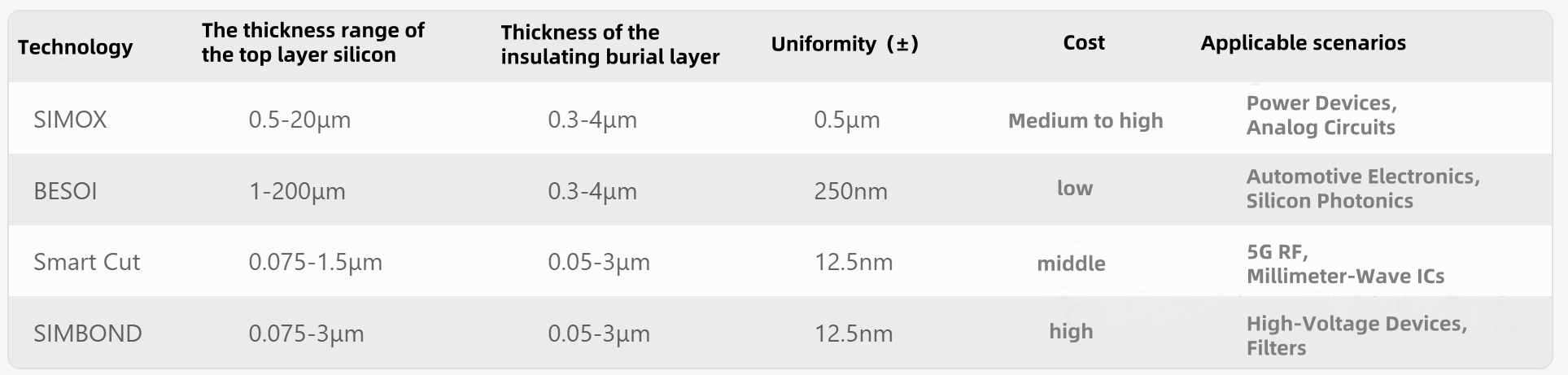

Nach der Herstellungstechnologie lassen sich die gängigen Prozesswege für SOI-Siliziumwafer wie folgt klassifizieren: SIMOX (Sauerstoffinjektions-Isolationstechnologie), BESOI (Bonding Thinning Technology) und Smart Cut (intelligent Stripping Technology).

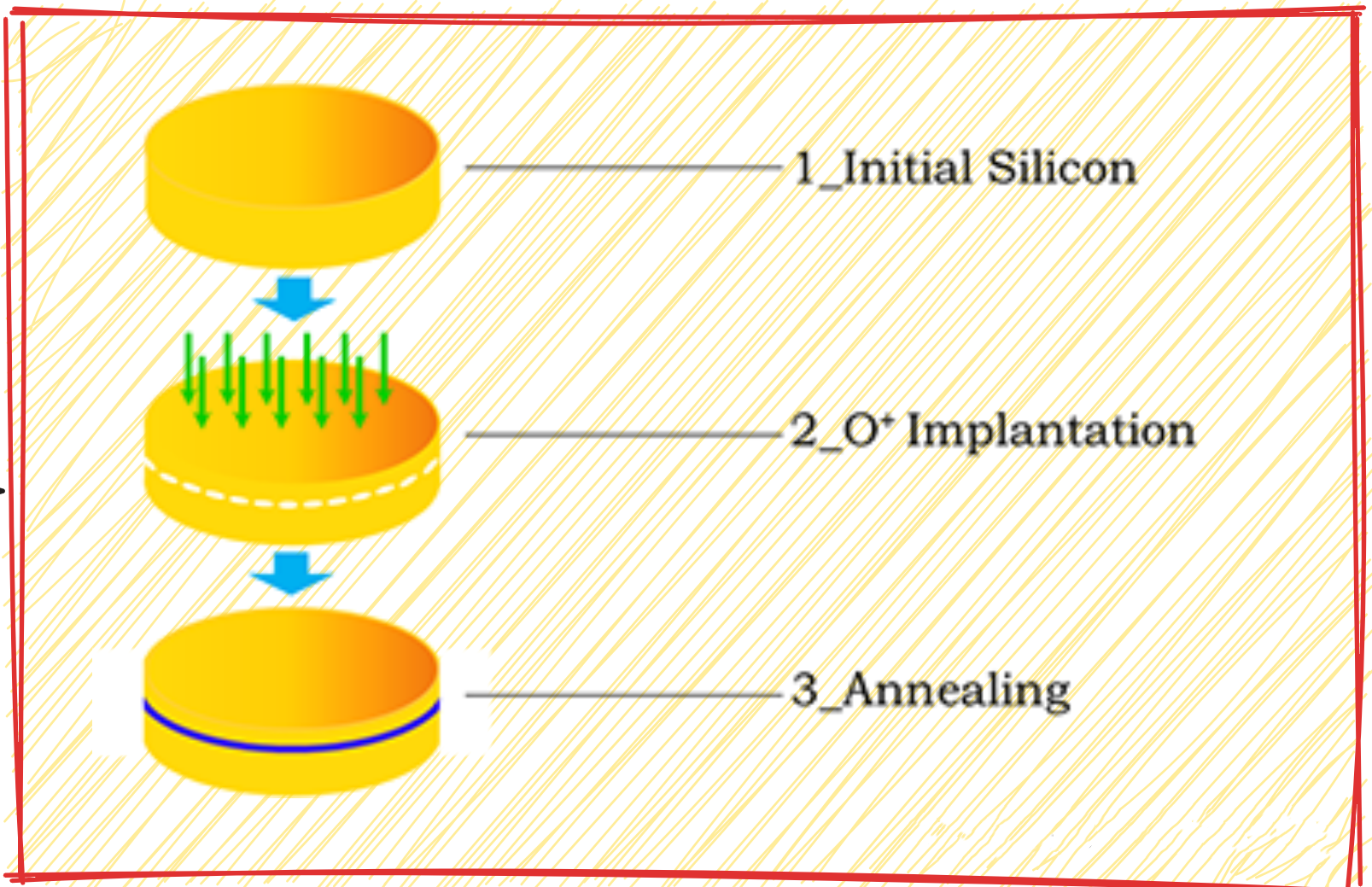

SIMOX (Oxygen Injection Isolation Technology) ist ein Verfahren, bei dem hochenergetische Sauerstoffionen in Siliziumwafer injiziert werden, um eine eingebettete Siliziumdioxidschicht zu bilden. Diese wird anschließend einer Hochtemperaturglühung unterzogen, um Gitterdefekte zu beheben. Kern des Verfahrens ist die direkte Sauerstoffioneninjektion zur Bildung einer vergrabenen Sauerstoffschicht.

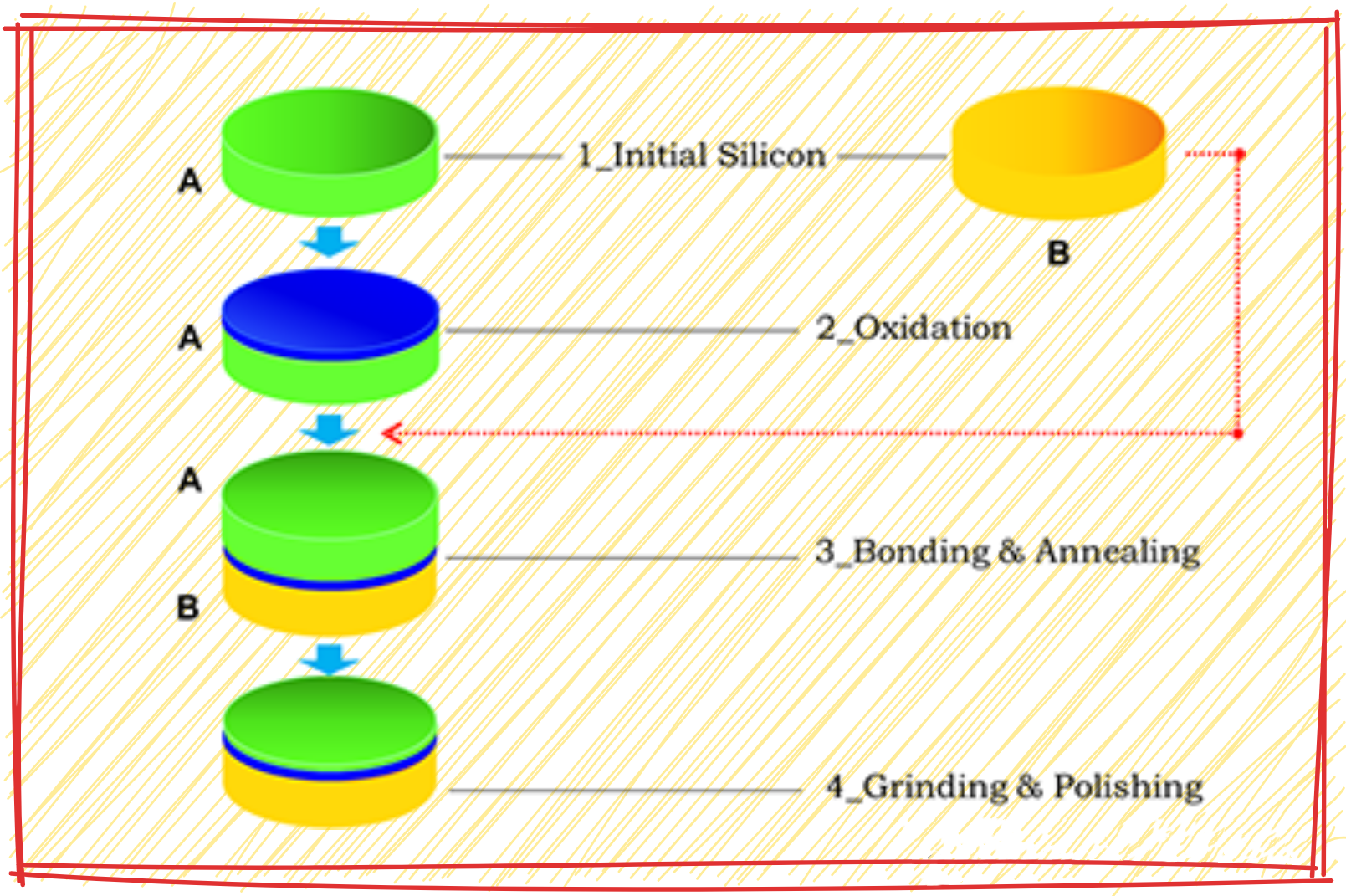

BESOI (Bonding Thinning Technology) beinhaltet das Verbinden zweier Siliziumwafer und das anschließende Ausdünnen eines davon durch mechanisches Schleifen und chemisches Ätzen, um eine SOI-Struktur zu erzeugen. Der Kern des Verfahrens liegt im Verbinden und Ausdünnen.

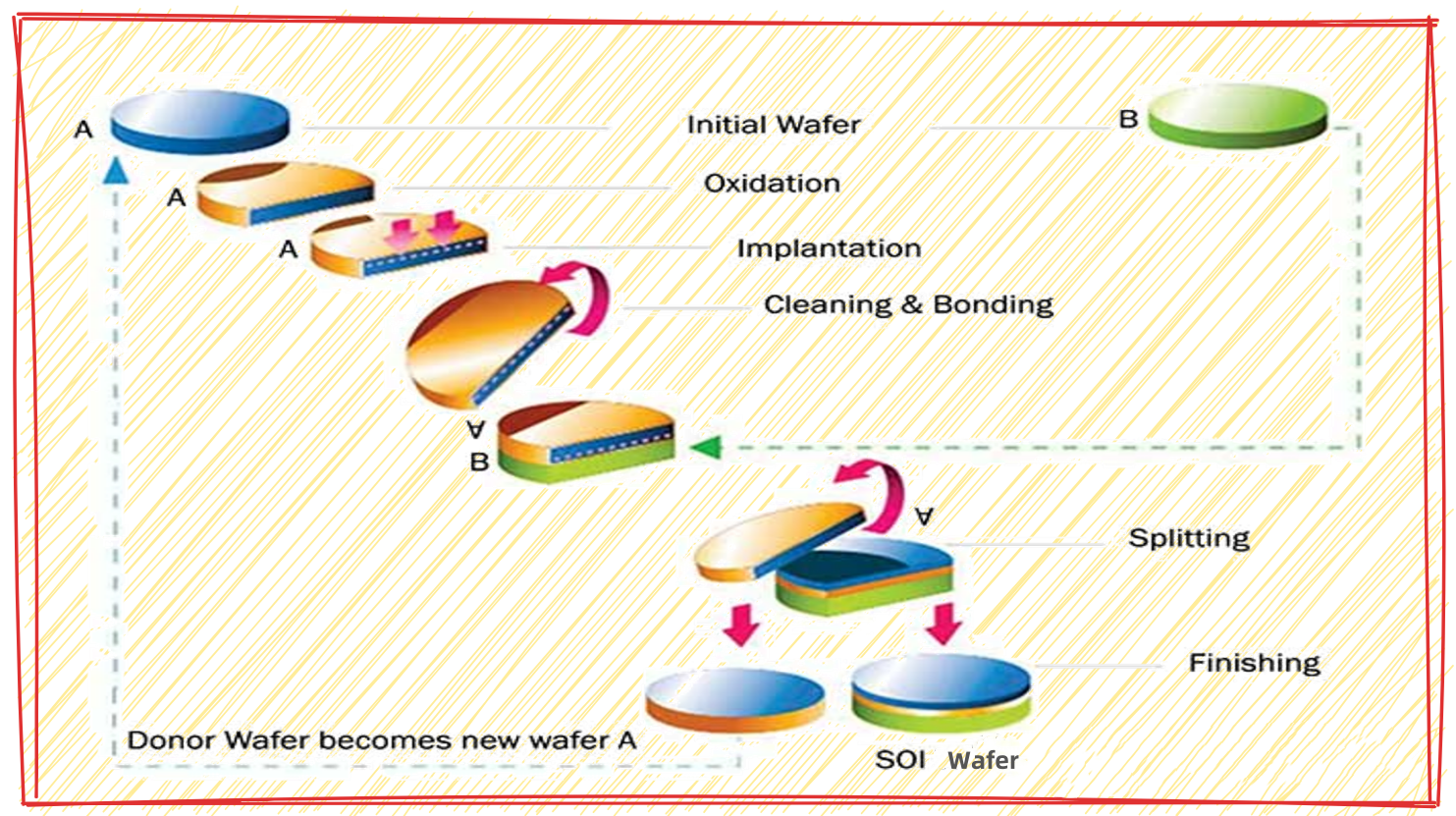

Smart Cut (Intelligente Exfoliationstechnologie) erzeugt durch Wasserstoffioneninjektion eine Exfoliationsschicht. Nach dem Bonden wird eine Wärmebehandlung durchgeführt, um den Siliziumwafer entlang der Wasserstoffionenschicht zu exfolieren und so eine ultradünne Siliziumschicht zu erzeugen. Kern des Verfahrens ist das Ablösen mittels Wasserstoffinjektion.

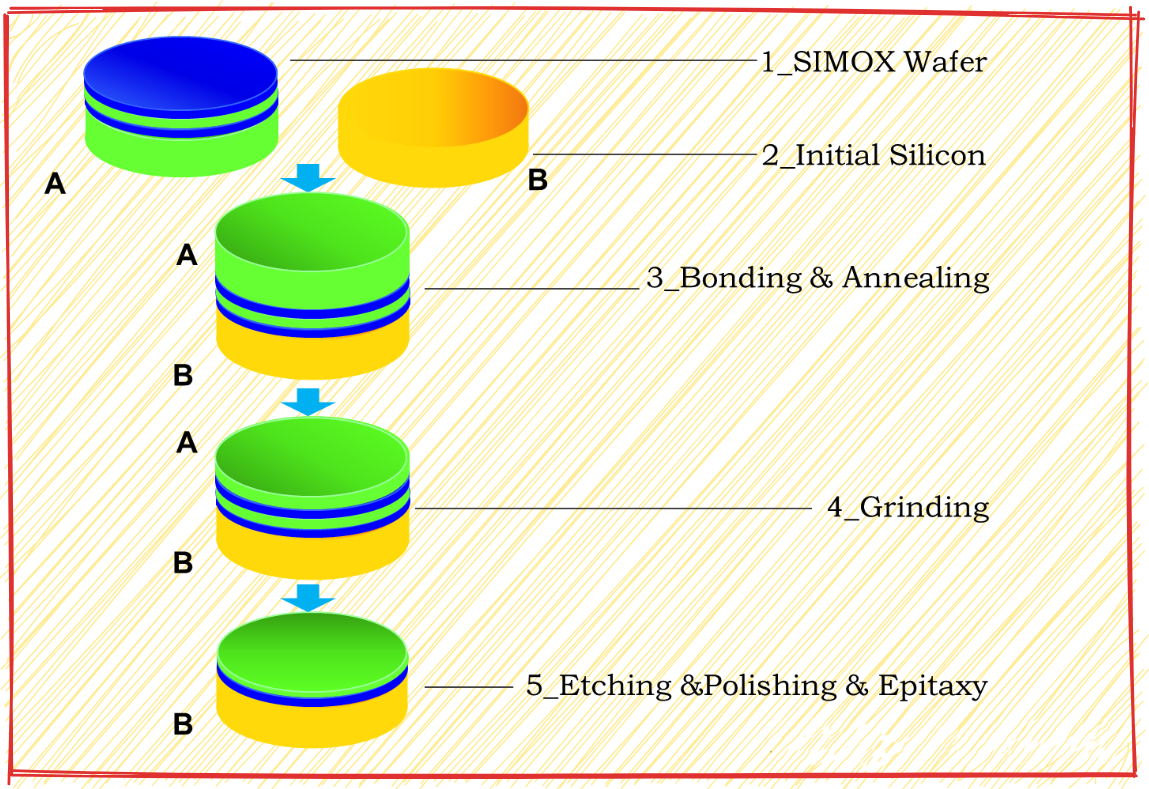

Aktuell existiert eine weitere Technologie namens SIMBOND (Sauerstoffinjektionsbondierung), die von Xinao entwickelt wurde. Dabei handelt es sich um ein Verfahren, das Sauerstoffinjektionsisolation und Bonding kombiniert. Der injizierte Sauerstoff dient als dünne Barriereschicht, während die eigentliche Sauerstoffschicht eine thermische Oxidationsschicht bildet. Dadurch werden gleichzeitig Parameter wie die Gleichmäßigkeit des oberen Siliziums und die Qualität der Sauerstoffschicht verbessert.

SOI-Siliziumwafer, die nach unterschiedlichen technischen Verfahren hergestellt werden, weisen unterschiedliche Leistungsparameter auf und eignen sich für verschiedene Anwendungsszenarien.

Die folgende Tabelle fasst die wichtigsten Leistungsvorteile von SOI-Siliziumwafern zusammen, kombiniert mit ihren technischen Merkmalen und praktischen Anwendungsszenarien. Im Vergleich zu herkömmlichem Bulk-Silizium bietet SOI deutliche Vorteile hinsichtlich des Verhältnisses von Geschwindigkeit und Energieverbrauch. (PS: Die Leistung von 22-nm-FD-SOI ist vergleichbar mit der von FinFET, die Kosten sind jedoch um 30 % reduziert.)

| Leistungsvorteil | Technisches Prinzip | Spezifische Manifestation | Typische Anwendungsszenarien |

| Niedrige parasitäre Kapazität | Die Isolierschicht (BOX) verhindert die Ladungskopplung zwischen Bauelement und Substrat. | Die Schaltgeschwindigkeit wurde um 15–30 % erhöht, der Stromverbrauch um 20–50 % reduziert. | 5G RF, Hochfrequenz-Kommunikationschips |

| Reduzierter Leckstrom | Die Isolierschicht unterdrückt Leckstrompfade | Leckstrom um >90 % reduziert, Batterielebensdauer verlängert | IoT-Geräte, tragbare Elektronik |

| Erhöhte Strahlungshärte | Die Isolierschicht verhindert die durch Strahlung verursachte Ladungsansammlung | Die Strahlungstoleranz wurde um das 3- bis 5-Fache verbessert, die Anzahl von Einzelereignissen wurde reduziert. | Raumfahrzeuge, Ausrüstung der Nuklearindustrie |

| Kurzkanal-Effektsteuerung | Eine dünne Siliziumschicht reduziert elektrische Feldstörungen zwischen Drain und Source. | Verbesserte Schwellenspannungsstabilität, optimierte Subthreshold-Steilheit | Fortschrittliche Knotenlogikchips (<14nm) |

| Verbessertes Wärmemanagement | Die Isolierschicht reduziert die Wärmeleitungskopplung | 30 % weniger Wärmestau, 15–25 °C niedrigere Betriebstemperatur | 3D-ICs, Automobilelektronik |

| Hochfrequenzoptimierung | Reduzierte parasitäre Kapazität und erhöhte Ladungsträgermobilität | 20 % geringere Verzögerung, unterstützt Signalverarbeitung >30 GHz | Millimeterwellenkommunikation, Satellitenkommunikationschips |

| Erhöhte Designflexibilität | Kein Brunnendoping erforderlich, unterstützt Backbiasing | 13–20 % weniger Prozessschritte, 40 % höhere Integrationsdichte | Mixed-Signal-ICs, Sensoren |

| Immunität gegen das Einrasten | Isolierschicht isoliert parasitäre PN-Übergänge | Latch-up-Stromschwelle auf >100 mA erhöht | Hochspannungs-Leistungsgeräte |

Zusammenfassend lässt sich sagen, dass die Hauptvorteile von SOI darin bestehen, dass es schnell arbeitet und energieeffizienter ist.

Aufgrund dieser Leistungsmerkmale findet SOI breite Anwendung in Bereichen, die eine ausgezeichnete Frequenz- und Leistungsaufnahmeleistung erfordern.

Wie unten dargestellt, lässt sich anhand des Anteils der Anwendungsbereiche, die SOI entsprechen, erkennen, dass HF- und Leistungselektronik den größten Teil des SOI-Marktes ausmachen.

| Anwendungsgebiet | Marktanteil |

| RF-SOI (Radiofrequenz) | 45 % |

| Power SOI | 30 % |

| FD-SOI (Vollständig erschöpft) | 15% |

| Optisches SOI | 8% |

| Sensor SOI | 2% |

Mit dem Wachstum von Märkten wie der Mobilkommunikation und dem autonomen Fahren wird auch für SOI-Siliziumwafer ein gewisses Wachstum erwartet.

XKH, ein führender Innovator im Bereich der SOI-Wafertechnologie (Silicon-on-Insulator), bietet umfassende SOI-Lösungen von der Forschung und Entwicklung bis zur Serienproduktion mit branchenführenden Fertigungsprozessen. Unser Portfolio umfasst 200-mm- und 300-mm-SOI-Wafer in den Varianten RF-SOI, Power-SOI und FD-SOI. Strenge Qualitätskontrollen gewährleisten eine außergewöhnliche Leistungskonstanz (Dickengleichmäßigkeit innerhalb von ±1,5 %). Wir bieten kundenspezifische Lösungen mit BOX-Schichtdicken (Buried Oxide) von 50 nm bis 1,5 µm und verschiedenen spezifischen Widerstandswerten, um spezifische Anforderungen zu erfüllen. Dank 15 Jahren technischer Expertise und einer robusten globalen Lieferkette liefern wir weltweit führende Halbleiterhersteller zuverlässig hochwertige SOI-Substratmaterialien und ermöglichen so innovative Chipentwicklungen in den Bereichen 5G-Kommunikation, Automobilelektronik und Künstliche Intelligenz.

Veröffentlichungsdatum: 24. April 2025