Zusammenfassung des SiC-Wafers

Siliziumkarbid (SiC)-WaferNano-Epitaxieschichten (Epitaxieschichten) haben sich als bevorzugtes Substrat für Hochleistungs-, Hochfrequenz- und Hochtemperaturelektronik in den Bereichen Automobil, erneuerbare Energien und Luft- und Raumfahrt etabliert. Unser Portfolio umfasst wichtige Polytypen und Dotierungsschemata – stickstoffdotiertes 4H (4H-N), hochreines halbisolierendes (HPSI), stickstoffdotiertes 3C (3C-N) und p-leitendes 4H/6H (4H/6H-P) – in drei Qualitätsstufen: PRIME (vollständig polierte Substrate in Bauelementqualität), DUMMY (geläppt oder unpoliert für Prozessversuche) und RESEARCH (kundenspezifische Epitaxieschichten und Dotierungsprofile für Forschung und Entwicklung). Die Waferdurchmesser reichen von 2″, 4″, 6″, 8″ bis 12″ und eignen sich sowohl für ältere Anlagen als auch für moderne Halbleiterfertigungsanlagen. Wir liefern außerdem monokristalline Boules und präzise orientierte Impfkristalle für das hauseigene Kristallwachstum.

Unsere 4H-N-Wafer weisen Ladungsträgerdichten von 1×10¹⁶ bis 1×10¹⁹ cm⁻³ und spezifische Widerstände von 0,01–10 Ω·cm auf und ermöglichen so eine exzellente Elektronenmobilität und Durchbruchfeldstärken über 2 MV/cm – ideal für Schottky-Dioden, MOSFETs und JFETs. HPSI-Substrate erreichen spezifische Widerstände von über 1×10¹² Ω·cm und Mikropipettendichten unter 0,1 cm⁻², wodurch minimale Leckströme für HF- und Mikrowellenbauelemente gewährleistet werden. Kubisches 3C-N, erhältlich in 2″- und 4″-Formaten, ermöglicht Heteroepitaxie auf Silizium und unterstützt neuartige photonische und MEMS-Anwendungen. P-leitende 4H/6H-P-Wafer, dotiert mit Aluminium auf 1×10¹⁶–5×10¹⁸ cm⁻³, ermöglichen komplementäre Bauelementarchitekturen.

SiC-Wafer der PRIME-Serie werden chemisch-mechanisch poliert und erreichen eine Oberflächenrauheit von <0,2 nm RMS, eine Gesamtdickenabweichung von unter 3 µm und eine Wölbung von <10 µm. DUMMY-Substrate beschleunigen Montage- und Verpackungstests, während RESEARCH-Wafer Epitaxieschichtdicken von 2–30 µm und eine kundenspezifische Dotierung aufweisen. Alle Produkte sind mittels Röntgenbeugung (Rocking-Kurve <30 Bogensekunden) und Raman-Spektroskopie zertifiziert. Elektrische Prüfungen – Hall-Messungen, C-V-Profilierung und Mikrokanal-Scanning – gewährleisten die Einhaltung der JEDEC- und SEMI-Normen.

Boules mit Durchmessern bis zu 150 mm werden mittels PVT und CVD mit Versetzungsdichten unter 1×10³ cm⁻² und geringer Anzahl an Mikropipetten gezüchtet. Die Impfkristalle werden innerhalb von 0,1° zur c-Achse geschnitten, um reproduzierbares Wachstum und hohe Schnittausbeuten zu gewährleisten.

Durch die Kombination mehrerer Polytypen, Dotierungsvarianten, Qualitätsstufen, SiC-Wafergrößen und der hauseigenen Boule- und Saatkristallproduktion optimiert unsere SiC-Substratplattform die Lieferketten und beschleunigt die Geräteentwicklung für Elektrofahrzeuge, intelligente Stromnetze und Anwendungen in rauen Umgebungen.

Zusammenfassung des SiC-Wafers

Siliziumkarbid (SiC)-WaferSiC-Wafer haben sich als bevorzugtes Substrat für Hochleistungs-, Hochfrequenz- und Hochtemperaturelektronik in den Bereichen Automobil, erneuerbare Energien und Luft- und Raumfahrt etabliert. Unser Portfolio umfasst wichtige Polytypen und Dotierungsschemata – stickstoffdotiertes 4H (4H-N), hochreines halbisolierendes (HPSI), stickstoffdotiertes 3C (3C-N) und p-leitendes 4H/6H (4H/6H-P) – angeboten in drei Qualitätsstufen.PRIME (vollständig polierte Substrate in Gerätequalität), DUMMY (geläppt oder unpoliert für Prozessversuche) und RESEARCH (kundenspezifische Epitaxieschichten und Dotierungsprofile für Forschung und Entwicklung). Die SiC-Wafer sind in Durchmessern von 2″, 4″, 6″, 8″ und 12″ erhältlich und eignen sich sowohl für ältere Anlagen als auch für moderne Halbleiterfertigungsanlagen. Wir liefern außerdem monokristalline Boules und präzise orientierte Impfkristalle für das hauseigene Kristallwachstum.

Unsere 4H-N-SiC-Wafer weisen Ladungsträgerdichten von 1×10¹⁶ bis 1×10¹⁹ cm⁻³ und spezifische Widerstände von 0,01–10 Ω·cm auf und bieten damit eine exzellente Elektronenmobilität und Durchbruchfeldstärken über 2 MV/cm – ideal für Schottky-Dioden, MOSFETs und JFETs. HPSI-Substrate erreichen spezifische Widerstände von über 1×10¹² Ω·cm und Mikropipettendichten unter 0,1 cm⁻², wodurch minimale Leckströme für HF- und Mikrowellenbauelemente gewährleistet werden. Kubisches 3C-N, erhältlich in 2″- und 4″-Formaten, ermöglicht Heteroepitaxie auf Silizium und unterstützt neuartige photonische und MEMS-Anwendungen. SiC-Wafer vom P-Typ 4H/6H-P, dotiert mit Aluminium auf 1×10¹⁶–5×10¹⁸ cm⁻³, ermöglichen komplementäre Gerätearchitekturen.

SiC-Wafer der PRIME-Serie werden chemisch-mechanisch poliert und erreichen eine Oberflächenrauheit von <0,2 nm (RMS), eine Gesamtdickenabweichung von unter 3 µm und eine Wölbung von <10 µm. DUMMY-Substrate beschleunigen Montage- und Verpackungstests, während RESEARCH-Wafer Epitaxieschichtdicken von 2–30 µm und eine kundenspezifische Dotierung aufweisen. Alle Produkte sind mittels Röntgenbeugung (Rocking-Kurve <30 Bogensekunden) und Raman-Spektroskopie zertifiziert. Elektrische Prüfungen – Hall-Messungen, C-V-Profilierung und Mikrokanal-Scanning – gewährleisten die Einhaltung der JEDEC- und SEMI-Normen.

Boules mit Durchmessern bis zu 150 mm werden mittels PVT und CVD mit Versetzungsdichten unter 1×10³ cm⁻² und geringer Anzahl an Mikropipetten gezüchtet. Die Impfkristalle werden innerhalb von 0,1° zur c-Achse geschnitten, um reproduzierbares Wachstum und hohe Schnittausbeuten zu gewährleisten.

Durch die Kombination mehrerer Polytypen, Dotierungsvarianten, Qualitätsstufen, SiC-Wafergrößen und der hauseigenen Boule- und Saatkristallproduktion optimiert unsere SiC-Substratplattform die Lieferketten und beschleunigt die Geräteentwicklung für Elektrofahrzeuge, intelligente Stromnetze und Anwendungen in rauen Umgebungen.

Datenblatt für 6-Zoll-SiC-Wafer vom Typ 4H-N

| Datenblatt für 6-Zoll-SiC-Wafer | ||||

| Parameter | Unterparameter | Z-Klasse | P-Note | Note D |

| Durchmesser | 149,5–150,0 mm | 149,5–150,0 mm | 149,5–150,0 mm | |

| Dicke | 4H‐N | 350 µm ± 15 µm | 350 µm ± 25 µm | 350 µm ± 25 µm |

| Dicke | 4H‐SI | 500 µm ± 15 µm | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Wafer-Ausrichtung | Außerhalb der Achse: 4,0° Richtung <11-20> ±0,5° (4H-N); Auf der Achse: <0001> ±0,5° (4H-SI) | Außerhalb der Achse: 4,0° Richtung <11-20> ±0,5° (4H-N); Auf der Achse: <0001> ±0,5° (4H-SI) | Außerhalb der Achse: 4,0° Richtung <11-20> ±0,5° (4H-N); Auf der Achse: <0001> ±0,5° (4H-SI) | |

| Mikrorohrdichte | 4H‐N | ≤ 0,2 cm⁻² | ≤ 2 cm⁻² | ≤ 15 cm⁻² |

| Mikrorohrdichte | 4H‐SI | ≤ 1 cm⁻² | ≤ 5 cm⁻² | ≤ 15 cm⁻² |

| Widerstand | 4H‐N | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | 0,015–0,028 Ω·cm |

| Widerstand | 4H‐SI | ≥ 1×10¹⁰ Ω·cm | ≥ 1×10⁵ Ω·cm | |

| Primäre flache Ausrichtung | [10-10] ± 5,0° | [10-10] ± 5,0° | [10-10] ± 5,0° | |

| Primäre Flachlänge | 4H‐N | 47,5 mm ± 2,0 mm | ||

| Primäre Flachlänge | 4H‐SI | Kerbe | ||

| Kantenausschluss | 3 mm | |||

| Warp/LTV/TTV/Bogen | ≤2,5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| Rauheit | Polieren | Ra ≤ 1 nm | ||

| Rauheit | CMP | Ra ≤ 0,2 nm | Ra ≤ 0,5 nm | |

| Randrisse | Keiner | Gesamtlänge ≤ 20 mm, Einzellänge ≤ 2 mm | ||

| Sechskantplatten | Kumulative Fläche ≤ 0,05 % | Kumulative Fläche ≤ 0,1 % | Kumulative Fläche ≤ 1 % | |

| Polytypbereiche | Keiner | Kumulative Fläche ≤ 3 % | Kumulative Fläche ≤ 3 % | |

| Kohlenstoffeinschlüsse | Kumulative Fläche ≤ 0,05 % | Kumulative Fläche ≤ 3 % | ||

| Oberflächenkratzer | Keiner | Gesamtlänge ≤ 1 × Waferdurchmesser | ||

| Kantenabsplitterungen | Keine zulässigen Abmessungen ≥ 0,2 mm Breite und Tiefe | Bis zu 7 Chips, jeweils ≤ 1 mm groß | ||

| TSD (Gewindeschrauben-Dislokation) | ≤ 500 cm⁻² | N / A | ||

| BPD (Basisebenenversetzung) | ≤ 1000 cm⁻² | N / A | ||

| Oberflächenverunreinigung | Keiner | |||

| Verpackung | Mehrfachwafer-Kassette oder Einzelwafer-Behälter | Mehrfachwafer-Kassette oder Einzelwafer-Behälter | Mehrfachwafer-Kassette oder Einzelwafer-Behälter | |

Datenblatt für 4-Zoll-SiC-Wafer vom Typ 4H-N

| Datenblatt für 4-Zoll-SiC-Wafer | |||

| Parameter | Null MPD-Produktion | Standardproduktionsqualität (P-Qualität) | Dummy-Note (Note D) |

| Durchmesser | 99,5 mm–100,0 mm | ||

| Dicke (4H-N) | 350 µm ± 15 µm | 350 µm ± 25 µm | |

| Dicke (4H-Si) | 500 µm ± 15 µm | 500 µm ± 25 µm | |

| Wafer-Ausrichtung | Abweichung von der Achse: 4,0° in Richtung <1120> ±0,5° für 4H-N; Abweichung von der Achse: <0001> ±0,5° für 4H-Si | ||

| Mikrorohrdichte (4H-N) | ≤0,2 cm⁻² | ≤2 cm⁻² | ≤15 cm⁻² |

| Mikrorohrdichte (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Spezifischer Widerstand (4H-N) | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | |

| Spezifischer Widerstand (4H-Si) | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |

| Primäre flache Ausrichtung | [10-10] ±5,0° | ||

| Primäre Flachlänge | 32,5 mm ±2,0 mm | ||

| Sekundäre Flachlänge | 18,0 mm ±2,0 mm | ||

| Sekundäre flache Ausrichtung | Siliziumseite nach oben: 90° im Uhrzeigersinn von der Grundfläche ±5,0° | ||

| Kantenausschluss | 3 mm | ||

| LTV/TTV/Bogenverwindung | ≤2,5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rauheit | Polierte Oberfläche Ra ≤1 nm; CMP-Oberfläche Ra ≤0,2 nm | Ra ≤0,5 nm | |

| Kantenrisse durch hochintensives Licht | Keiner | Keiner | Gesamtlänge ≤10 mm; Einzellänge ≤2 mm |

| Sechseckige Platten durch Hochleistungslicht | Kumulative Fläche ≤0,05% | Kumulative Fläche ≤0,05% | Kumulative Fläche ≤0,1% |

| Polytypbereiche durch hochintensives Licht | Keiner | Kumulative Fläche ≤3% | |

| Visuelle Kohlenstoffeinschlüsse | Kumulative Fläche ≤0,05% | Kumulative Fläche ≤3% | |

| Kratzer auf Silikonoberflächen durch hochintensives Licht | Keiner | Kumulative Länge ≤1 Waferdurchmesser | |

| Kantensplitter durch hochintensives Licht | Keine zulässige Breite und Tiefe ≥ 0,2 mm. | 5 zulässig, jeweils ≤1 mm | |

| Siliziumoberflächenkontamination durch hochintensives Licht | Keiner | ||

| Gewindeschraubenverschiebung | ≤500 cm⁻² | N / A | |

| Verpackung | Mehrfachwafer-Kassette oder Einzelwafer-Behälter | Mehrfachwafer-Kassette oder Einzelwafer-Behälter | Mehrfachwafer-Kassette oder Einzelwafer-Behälter |

Datenblatt für 4-Zoll-HPSI-SiC-Wafer

| Datenblatt für 4-Zoll-HPSI-SiC-Wafer | |||

| Parameter | Null MPD Produktionsklasse (Z-Klasse) | Standardproduktionsqualität (P-Qualität) | Dummy-Note (Note D) |

| Durchmesser | 99,5–100,0 mm | ||

| Dicke (4H-Si) | 500 µm ±20 µm | 500 µm ±25 µm | |

| Wafer-Ausrichtung | Abweichung von der Achse: 4,0° in Richtung <11-20> ±0,5° für 4H-N; Abweichung von der Achse: <0001> ±0,5° für 4H-Si | ||

| Mikrorohrdichte (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Spezifischer Widerstand (4H-Si) | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |

| Primäre flache Ausrichtung | (10-10) ±5,0° | ||

| Primäre Flachlänge | 32,5 mm ±2,0 mm | ||

| Sekundäre Flachlänge | 18,0 mm ±2,0 mm | ||

| Sekundäre flache Ausrichtung | Siliziumseite nach oben: 90° im Uhrzeigersinn von der Grundfläche ±5,0° | ||

| Kantenausschluss | 3 mm | ||

| LTV/TTV/Bogenverwindung | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rauheit (C-Fläche) | Polieren | Ra ≤1 nm | |

| Rauheit (Si-Oberfläche) | CMP | Ra ≤0,2 nm | Ra ≤0,5 nm |

| Kantenrisse durch hochintensives Licht | Keiner | Gesamtlänge ≤10 mm; Einzellänge ≤2 mm | |

| Sechseckige Platten durch Hochleistungslicht | Kumulative Fläche ≤0,05% | Kumulative Fläche ≤0,05% | Kumulative Fläche ≤0,1% |

| Polytypbereiche durch hochintensives Licht | Keiner | Kumulative Fläche ≤3% | |

| Visuelle Kohlenstoffeinschlüsse | Kumulative Fläche ≤0,05% | Kumulative Fläche ≤3% | |

| Kratzer auf Silikonoberflächen durch hochintensives Licht | Keiner | Kumulative Länge ≤1 Waferdurchmesser | |

| Kantensplitter durch hochintensives Licht | Keine zulässige Breite und Tiefe ≥ 0,2 mm. | 5 zulässig, jeweils ≤1 mm | |

| Siliziumoberflächenkontamination durch hochintensives Licht | Keiner | Keiner | |

| Gewindeschraubenverschiebung | ≤500 cm⁻² | N / A | |

| Verpackung | Mehrfachwafer-Kassette oder Einzelwafer-Behälter | ||

Anwendung von SiC-Wafern

-

SiC-Wafer-Leistungsmodule für Wechselrichter von Elektrofahrzeugen

Auf hochwertigen SiC-Wafer-Substraten gefertigte MOSFETs und Dioden zeichnen sich durch extrem niedrige Schaltverluste aus. Dank der SiC-Wafer-Technologie arbeiten diese Leistungsmodule bei höheren Spannungen und Temperaturen und ermöglichen so effizientere Traktionswechselrichter. Die Integration von SiC-Wafer-Chips in Leistungsstufen reduziert den Kühlbedarf und die benötigte Fläche und demonstriert damit das volle Potenzial der SiC-Wafer-Innovation. -

Hochfrequenz-HF- und 5G-Bauelemente auf SiC-Wafer

Auf halbisolierenden SiC-Wafern gefertigte HF-Verstärker und -Schalter zeichnen sich durch überlegene Wärmeleitfähigkeit und Durchbruchspannung aus. Das SiC-Wafer-Substrat minimiert dielektrische Verluste im GHz-Bereich, während seine Materialfestigkeit einen stabilen Betrieb unter Hochleistungs- und Hochtemperaturbedingungen ermöglicht. Dadurch ist der SiC-Wafer das Substrat der Wahl für 5G-Basisstationen und Radarsysteme der nächsten Generation. -

Optoelektronische und LED-Substrate aus SiC-Wafer

Blaue und UV-LEDs, die auf SiC-Wafer-Substraten gewachsen werden, profitieren von exzellenter Gitteranpassung und Wärmeableitung. Die Verwendung eines polierten C-Flächen-SiC-Wafers gewährleistet gleichmäßige Epitaxieschichten, während die inhärente Härte des SiC-Wafers ein präzises Wafer-Dünnen und eine zuverlässige Bauteilintegration ermöglicht. Dies macht den SiC-Wafer zur idealen Plattform für Hochleistungs-LED-Anwendungen mit langer Lebensdauer.

Fragen und Antworten zu SiC-Wafern

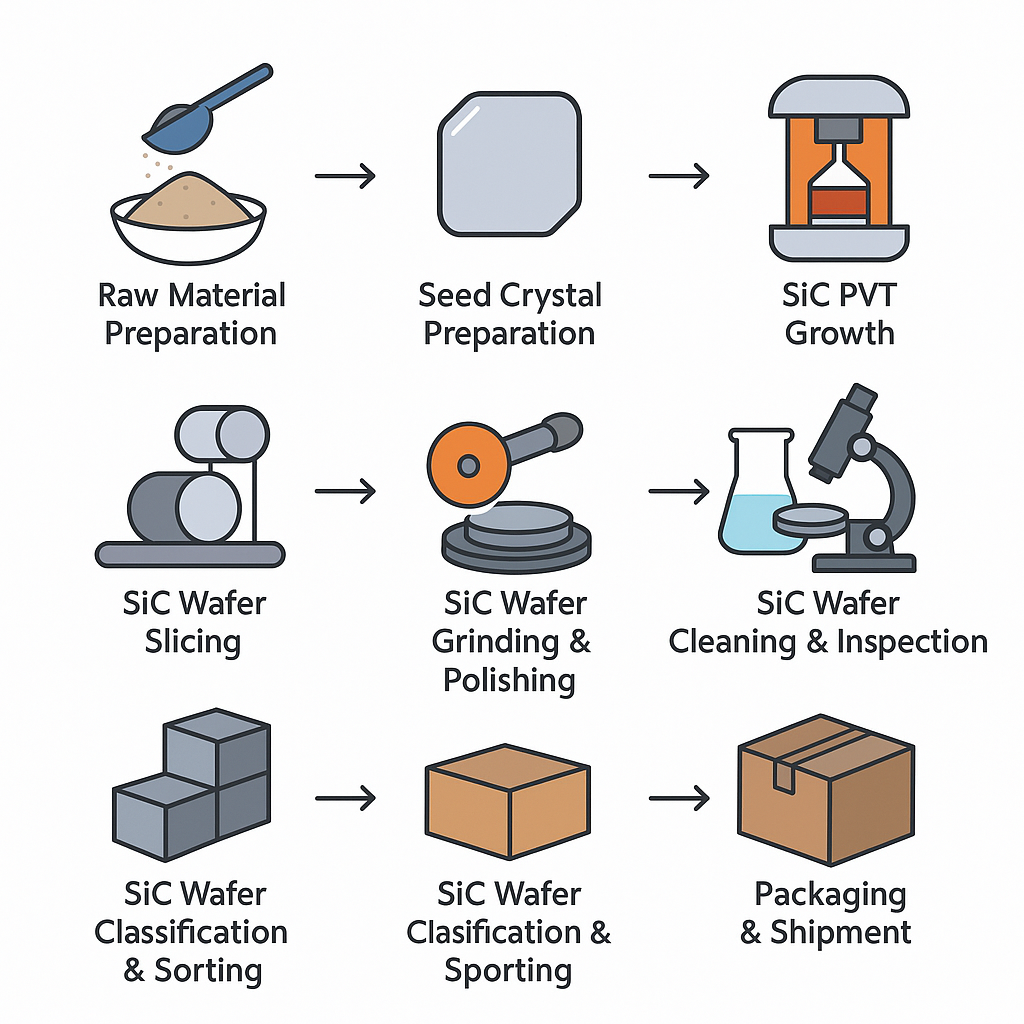

1. F: Wie werden SiC-Wafer hergestellt?

A:

hergestellte SiC-WaferDetaillierte Schritte

-

SiC-WaferRohmaterialvorbereitung

- Verwenden Sie SiC-Pulver der Güteklasse ≥5N (Verunreinigungen ≤1 ppm).

- Sieben und vorbacken, um restliche Kohlenstoff- oder Stickstoffverbindungen zu entfernen.

-

SiCImpfkristallpräparation

-

Man nehme ein Stück 4H-SiC-Einkristall und schneide es entlang der 〈0001〉-Orientierung auf eine Größe von etwa 10 × 10 mm².

-

Präzisionspolieren bis zu Ra ≤0,1 nm und Markierung der Kristallorientierung.

-

-

SiCPVT-Wachstum (Physikalischer Dampftransport)

-

Graphittiegel befüllen: unten mit SiC-Pulver, oben mit Impfkristall.

-

Evakuieren Sie auf 10⁻³–10⁻⁵ Torr oder füllen Sie mit hochreinem Helium bei 1 atm auf.

-

Die Wärmequellenzone sollte auf 2100–2300 ℃ erhitzt werden, die Saatzone sollte 100–150 ℃ kühler bleiben.

-

Die Wachstumsrate sollte bei 1–5 mm/h kontrolliert werden, um ein Gleichgewicht zwischen Qualität und Durchsatz zu erreichen.

-

-

SiCBarrenglühen

-

Den frisch hergestellten SiC-Ingot bei 1600–1800 ℃ für 4–8 Stunden ausglühen.

-

Ziel: Abbau von thermischen Spannungen und Reduzierung der Versetzungsdichte.

-

-

SiCWaffelschneiden

-

Verwenden Sie eine Diamantdrahtsäge, um den Barren in 0,5–1 mm dicke Scheiben zu schneiden.

-

Um Mikrorisse zu vermeiden, sollten Vibrationen und seitliche Kräfte minimiert werden.

-

-

SiCWaferSchleifen & Polieren

-

Grobmahlenum Sägeschäden zu beseitigen (Rauheit ~10–30 µm).

-

Feinmahlenum eine Ebenheit von ≤5 µm zu erreichen.

-

Chemisch-mechanisches Polieren (CMP)um eine spiegelähnliche Oberfläche (Ra ≤0,2 nm) zu erreichen.

-

-

SiCWaferReinigung und Inspektion

-

Ultraschallreinigungin Piranha-Lösung (H₂SO₄:H₂O₂), entionisiertem Wasser, dann IPA.

-

XRD/Raman-Spektroskopieum den Polytyp (4H, 6H, 3C) zu bestätigen.

-

Interferometriezur Messung der Ebenheit (<5 µm) und der Verformung (<20 µm).

-

Vierpunktsondezum Testen des spezifischen Widerstands (z. B. HPSI ≥10⁹ Ω·cm).

-

Fehlerprüfungunter einem Polarisationsmikroskop und einem Ritzprüfgerät.

-

-

SiCWaferKlassifizierung & Sortierung

-

Wafer nach Polytyp und elektrischem Typ sortieren:

-

4H-SiC N-Typ (4H-N): Ladungsträgerkonzentration 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC hochreines halbisolierendes Material (4H-HPSI): spezifischer Widerstand ≥10⁹ Ω·cm

-

6H-SiC N-Typ (6H-N)

-

Andere: 3C-SiC, P-Typ usw.

-

-

-

SiCWaferVerpackung & Versand

2. F: Was sind die wichtigsten Vorteile von SiC-Wafern gegenüber Siliziumwafern?

A: Im Vergleich zu Siliziumwafern ermöglichen SiC-Wafer Folgendes:

-

Betrieb mit höherer Spannung(>1.200 V) mit niedrigerem Einschaltwiderstand.

-

Höhere Temperaturstabilität(>300 °C) und verbessertes Wärmemanagement.

-

Schnellere Schaltgeschwindigkeitenmit geringeren Schaltverlusten, wodurch die Kühlung auf Systemebene und die Größe der Leistungswandler reduziert werden.

4. Frage: Welche häufigen Defekte beeinträchtigen die Ausbeute und Leistung von SiC-Wafern?

A: Zu den Hauptdefekten in SiC-Wafern zählen Mikrokanäle, Basisebenenversetzungen (BPDs) und Oberflächenkratzer. Mikrokanäle können zu einem katastrophalen Geräteausfall führen; BPDs erhöhen den Durchlasswiderstand mit der Zeit; und Oberflächenkratzer führen zu Waferbruch oder schlechtem Epitaxiewachstum. Sorgfältige Inspektion und Defektminimierung sind daher unerlässlich, um die Ausbeute an SiC-Wafern zu maximieren.

Veröffentlichungsdatum: 30. Juni 2025